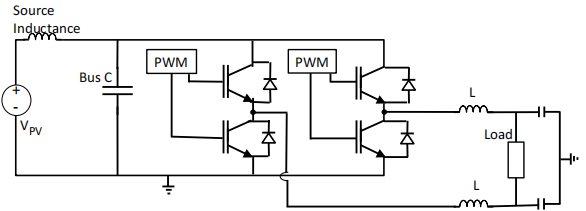

ઇન્વર્ટરનો હેતુ ડીસી વેવફોર્મ વોલ્ટેજને એસી સિગ્નલમાં રૂપાંતરિત કરવાનો છે જેથી આપેલ ફ્રીક્વન્સી પર અને નાના ફેઝ એંગલ સાથે લોડ (દા.ત. પાવર ગ્રીડ) માં પાવર ઇન્જેક્ટ કરી શકાય (φ ≈0). સિંગલ ફેઝ યુનિપોલર પલ્સ-વિડ્થ મોડ્યુલેશન (PWM) માટે એક સરળ સર્કિટ આકૃતિમાં બતાવવામાં આવી છે.2 (આ જ સામાન્ય યોજના ત્રણ તબક્કાની સિસ્ટમ સુધી વિસ્તૃત કરી શકાય છે). આ યોજનામાં, એક પીવી સિસ્ટમ, જે કેટલાક સ્રોત ઇન્ડક્ટન્સ સાથે ડીસી વોલ્ટેજ સ્ત્રોત તરીકે કાર્ય કરે છે, તેને ફ્રીવ્હીલિંગ ડાયોડ સાથે સમાંતર ચાર IGBT સ્વીચો દ્વારા AC સિગ્નલમાં આકાર આપવામાં આવે છે. આ સ્વીચોને PWM સિગ્નલ દ્વારા ગેટ પર નિયંત્રિત કરવામાં આવે છે, જે સામાન્ય રીતે IC નું આઉટપુટ હોય છે જે વાહક તરંગ (સામાન્ય રીતે ઇચ્છિત આઉટપુટ આવર્તનનો સાઈન તરંગ) અને નોંધપાત્ર રીતે વધુ આવર્તન (સામાન્ય રીતે 5-20kHz પર ત્રિકોણ તરંગ) પર સંદર્ભ તરંગની તુલના કરે છે. LC ફિલ્ટર્સના વિવિધ ટોપોલોજીના ઉપયોગ દ્વારા IGBTs ના આઉટપુટને ઉપયોગ અથવા ગ્રીડ ઇન્જેક્શન માટે યોગ્ય AC સિગ્નલમાં આકાર આપવામાં આવે છે.

ઇન્વર્ટર સ્ટેટિક કન્વર્ટરના મોટા જૂથના છે, જેમાં આજના ઘણાનો સમાવેશ થાય છે'ઉપકરણો સક્ષમ છે"કન્વર્ટ કરો"ઇનપુટમાં વિદ્યુત પરિમાણો, જેમ કે વોલ્ટેજ અને ફ્રીક્વન્સી, જેથી લોડની જરૂરિયાતો સાથે સુસંગત આઉટપુટ ઉત્પન્ન કરી શકાય.

સામાન્ય રીતે કહીએ તો, ઇન્વર્ટર એવા ઉપકરણો છે જે ડાયરેક્ટ કરંટને વૈકલ્પિક કરંટમાં રૂપાંતરિત કરવામાં સક્ષમ છે અને ઔદ્યોગિક ઓટોમેશન એપ્લિકેશન્સ અને ઇલેક્ટ્રિક ડ્રાઇવ્સમાં ખૂબ સામાન્ય છે. વિવિધ ઇન્વર્ટર પ્રકારના આર્કિટેક્ચર અને ડિઝાઇન દરેક ચોક્કસ એપ્લિકેશન અનુસાર બદલાય છે, ભલે તેમના મુખ્ય હેતુનો મુખ્ય ભાગ સમાન હોય (DC થી AC રૂપાંતર).

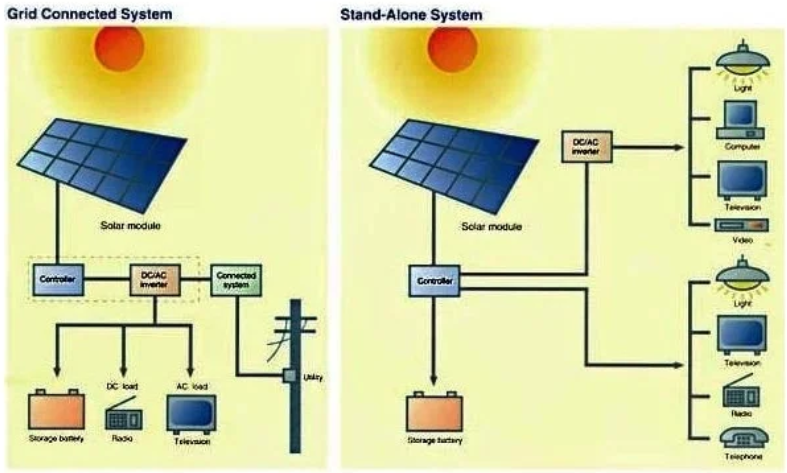

૧. સ્ટેન્ડઅલોન અને ગ્રીડ-કનેક્ટેડ ઇન્વર્ટર

ફોટોવોલ્ટેઇક એપ્લિકેશન્સમાં ઉપયોગમાં લેવાતા ઇન્વર્ટરને ઐતિહાસિક રીતે બે મુખ્ય શ્રેણીઓમાં વિભાજિત કરવામાં આવ્યા છે:

:સ્ટેન્ડઅલોન ઇન્વર્ટર

:ગ્રીડ-કનેક્ટેડ ઇન્વર્ટર

સ્ટેન્ડઅલોન ઇન્વર્ટર એવા ઉપયોગો માટે છે જ્યાં પીવી પ્લાન્ટ મુખ્ય ઉર્જા વિતરણ નેટવર્ક સાથે જોડાયેલ નથી. ઇન્વર્ટર મુખ્ય વિદ્યુત પરિમાણો (વોલ્ટેજ અને આવર્તન) ની સ્થિરતા સુનિશ્ચિત કરીને, કનેક્ટેડ લોડ્સને વિદ્યુત ઉર્જા પૂરી પાડવા સક્ષમ છે. આ તેમને પૂર્વનિર્ધારિત મર્યાદામાં રાખે છે, કામચલાઉ ઓવરલોડિંગ પરિસ્થિતિઓનો સામનો કરવા સક્ષમ છે. આ પરિસ્થિતિમાં, સતત ઉર્જા પુરવઠો સુનિશ્ચિત કરવા માટે ઇન્વર્ટરને બેટરી સ્ટોરેજ સિસ્ટમ સાથે જોડવામાં આવે છે.

બીજી બાજુ, ગ્રીડ-કનેક્ટેડ ઇન્વર્ટર, જે ઇલેક્ટ્રિકલ ગ્રીડ સાથે જોડાયેલા છે તેની સાથે સિંક્રનાઇઝ કરવામાં સક્ષમ છે કારણ કે, આ કિસ્સામાં, વોલ્ટેજ અને ફ્રીક્વન્સી"લાદેલું"મુખ્ય ગ્રીડ દ્વારા. મુખ્ય ગ્રીડના કોઈપણ સંભવિત રિવર્સ સપ્લાયને ટાળવા માટે, જો મુખ્ય ગ્રીડ નિષ્ફળ જાય તો આ ઇન્વર્ટર ડિસ્કનેક્ટ થવા સક્ષમ હોવા જોઈએ, જે ગંભીર જોખમનું પ્રતિનિધિત્વ કરી શકે છે.

- આકૃતિ 1 - સ્ટેન્ડઅલોન સિસ્ટમ અને ગ્રીડ-કનેક્ટેડ સિસ્ટમનું ઉદાહરણ. છબી સૌજન્ય બિબ્લસ.

2. બસ કેપેસિટરની ભૂમિકા શું છે?

આકૃતિ 2: પલ્સ્ડ વિડ્થ મોડ્યુલેશન (PWM) સિંગલ-ફેઝઇન્વર્ટર સેટઅપ. IGBT સ્વીચો, LC આઉટપુટ ફિલ્ટર સાથે, DC ઇનપુટ સિગ્નલને ઉપયોગી AC સિગ્નલમાં આકાર આપે છે. આનાથીપીવી ટર્મિનલ્સ પર હાનિકારક વોલ્ટેજ લહેર. બસઆ લહેર ઘટાડવા માટે કેપેસિટરનું કદ મોટું કરવામાં આવે છે.

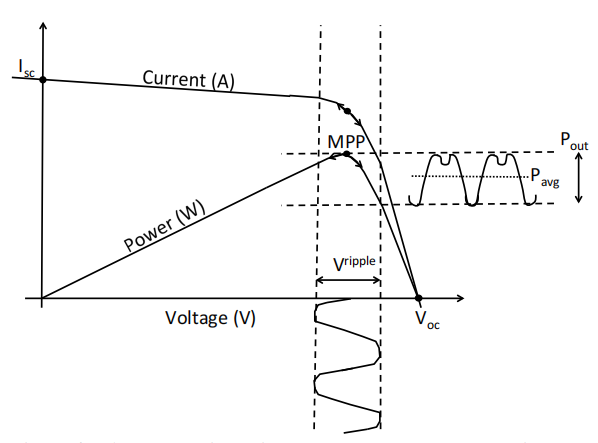

IGBTs નું સંચાલન PV એરેના ટર્મિનલ પર રિપલ વોલ્ટેજ રજૂ કરે છે. આ રિપલ PV સિસ્ટમના સંચાલન માટે હાનિકારક છે, કારણ કે ટર્મિનલ્સ પર લાગુ કરાયેલ નજીવો વોલ્ટેજ મહત્તમ પાવર એક્સટ્રેક્ટ કરવા માટે IV કર્વના મહત્તમ પાવર પોઈન્ટ (MPP) પર રાખવો જોઈએ. PV ટર્મિનલ્સ પર વોલ્ટેજ રિપલ સિસ્ટમમાંથી એક્સટ્રેક્ટેડ પાવરને ઓસીલેટ કરશે, પરિણામે

નીચું સરેરાશ પાવર આઉટપુટ (આકૃતિ 3). વોલ્ટેજ રિપલને સરળ બનાવવા માટે બસમાં એક કેપેસિટર ઉમેરવામાં આવે છે.

આકૃતિ 3: PWM ઇન્વર્ટર સ્કીમ દ્વારા PV ટર્મિનલ્સ પર દાખલ કરાયેલ વોલ્ટેજ રિપલ, PV એરેના મહત્તમ પાવર પોઈન્ટ (MPP) થી લાગુ વોલ્ટેજને ખસેડે છે. આ એરેના પાવર આઉટપુટમાં રિપલ રજૂ કરે છે જેથી સરેરાશ આઉટપુટ પાવર નોમિનલ MPP કરતા ઓછો હોય.

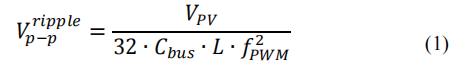

વોલ્ટેજ રિપલનું કંપનવિસ્તાર (ટોચથી ટોચ સુધી) સ્વિચિંગ ફ્રીક્વન્સી, પીવી વોલ્ટેજ, બસ કેપેસીટન્સ અને ફિલ્ટર ઇન્ડક્ટન્સ દ્વારા નક્કી કરવામાં આવે છે:

ક્યાં:

VPV એ સૌર પેનલ DC વોલ્ટેજ છે,

Cbus એ બસ કેપેસિટરનું કેપેસિટન્સ છે,

L એ ફિલ્ટર ઇન્ડક્ટર્સનું ઇન્ડક્ટન્સ છે,

fPWM એ સ્વિચિંગ ફ્રીક્વન્સી છે.

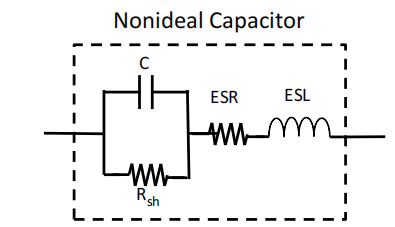

સમીકરણ (1) એક આદર્શ કેપેસિટર પર લાગુ પડે છે જે ચાર્જિંગ દરમિયાન કેપેસિટરમાંથી ચાર્જ વહેતો અટકાવે છે અને પછી કોઈ પ્રતિકાર વિના ઇલેક્ટ્રિક ક્ષેત્રમાં સ્થિત ઊર્જાને ડિસ્ચાર્જ કરે છે. વાસ્તવમાં, કોઈ પણ કેપેસિટર આદર્શ નથી (આકૃતિ 4) પરંતુ તે બહુવિધ તત્વોથી બનેલું છે. આદર્શ કેપેસિટન્સ ઉપરાંત, ડાઇલેક્ટ્રિક સંપૂર્ણ રીતે પ્રતિકારક નથી અને એક નાનો લિકેજ પ્રવાહ એનોડથી કેથોડમાં મર્યાદિત શન્ટ પ્રતિકાર (Rsh) સાથે વહે છે, જે ડાઇલેક્ટ્રિક કેપેસિટન્સ (C) ને બાયપાસ કરે છે. જ્યારે કેપેસિટરમાંથી પ્રવાહ વહેતો હોય છે, ત્યારે પિન, ફોઇલ અને ડાઇલેક્ટ્રિક સંપૂર્ણ રીતે વાહક નથી હોતા અને કેપેસિટન્સ સાથે શ્રેણીમાં સમકક્ષ શ્રેણી પ્રતિકાર (ESR) હોય છે. છેલ્લે, કેપેસિટર ચુંબકીય ક્ષેત્રમાં કેટલીક ઊર્જા સંગ્રહિત કરે છે, તેથી કેપેસિટન્સ અને ESR સાથે શ્રેણીમાં સમકક્ષ શ્રેણી ઇન્ડક્ટન્સ (ESL) હોય છે.

આકૃતિ 4: સામાન્ય કેપેસિટરનું સમકક્ષ સર્કિટ. એક કેપેસિટર છેઘણા બિન-આદર્શ તત્વોથી બનેલું છે, જેમાં ડાઇલેક્ટ્રિક કેપેસીટન્સ (C), કેપેસિટરને બાયપાસ કરતા ડાઇલેક્ટ્રિક દ્વારા બિન-અનંત શન્ટ પ્રતિકાર, શ્રેણી પ્રતિકાર (ESR), અને શ્રેણી ઇન્ડક્ટન્સ (ESL)નો સમાવેશ થાય છે.

કેપેસિટર જેવા સરળ દેખાતા ઘટકમાં પણ, ઘણા બધા તત્વો હોય છે જે નિષ્ફળ અથવા અધોગતિ પામી શકે છે. આ દરેક તત્વો AC અને DC બંને બાજુએ ઇન્વર્ટરના વર્તનને અસર કરી શકે છે. PV ટર્મિનલ્સમાં રજૂ કરાયેલા વોલ્ટેજ રિપલ પર બિન-આદર્શ કેપેસિટર ઘટકોના અધોગતિનો પ્રભાવ નક્કી કરવા માટે, SPICE નો ઉપયોગ કરીને PWM યુનિપોલર H-બ્રિજ ઇન્વર્ટર (આકૃતિ 2) નું સિમ્યુલેટર બનાવવામાં આવ્યું હતું. ફિલ્ટર કેપેસિટર્સ અને ઇન્ડક્ટર્સ અનુક્રમે 250µF અને 20mH પર રાખવામાં આવે છે. IGBTs માટે SPICE મોડેલ્સ પેટ્રી એટ અલના કાર્યમાંથી લેવામાં આવ્યા છે. PWM સિગ્નલ, જે IGBT સ્વીચોને નિયંત્રિત કરે છે, તે અનુક્રમે ઉચ્ચ અને નીચલા-બાજુ IGBT સ્વીચો માટે કમ્પેરેટર અને ઇન્વર્ટિંગ કમ્પેરેટર સર્કિટ દ્વારા નક્કી કરવામાં આવે છે. PWM નિયંત્રણો માટે ઇનપુટ 9.5V, 60Hz સાઈન કેરિયર વેવ અને 10V, 10kHz ત્રિકોણાકાર વેવ છે.

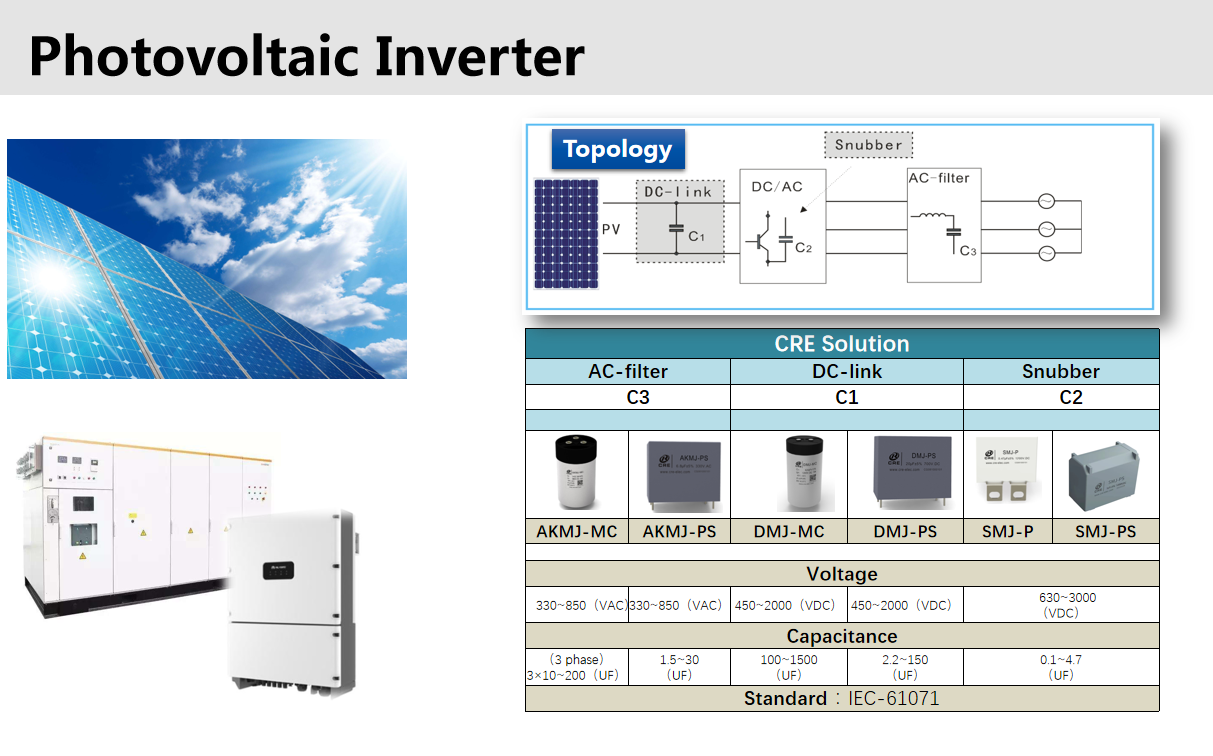

- CRE સોલ્યુશન

CRE એ એક હાઇ-ટેક એન્ટરપ્રાઇઝ છે જે ફિલ્મ કેપેસિટરના ઉત્પાદનમાં વિશેષતા ધરાવે છે, જે પાવર ઇલેક્ટ્રિકિઓનિક્સ પર ધ્યાન કેન્દ્રિત કરે છે.

CRE પીવી ઇન્વર્ટર માટે ફિલ્મ કેપેસિટર શ્રેણીનું પરિપક્વ સોલ્યુશન ઓફર કરે છે જેમાં DC-લિંક, AC-ફિલ્ટર અને સ્નબરનો સમાવેશ થાય છે.

પોસ્ટ સમય: ડિસેમ્બર-01-2023